Transistor-evolusjon: Fra plan til CFET, 3D-integrasjon redefinerer halvlederfremgang

I mer enn et halvt århundre vokste halvlederindustrien ved å følge en enkel regel: gjør transistorer mindre.Krympende funksjonsstørrelser ga høyere ytelse, lavere effekt og lavere kostnad per transistor.Men i dag har denne veien nådd sin fysiske og økonomiske grense.Tiden med ren skalering er over, og en ny æra av strukturell innovasjon og 3D-integrasjon har begynt.

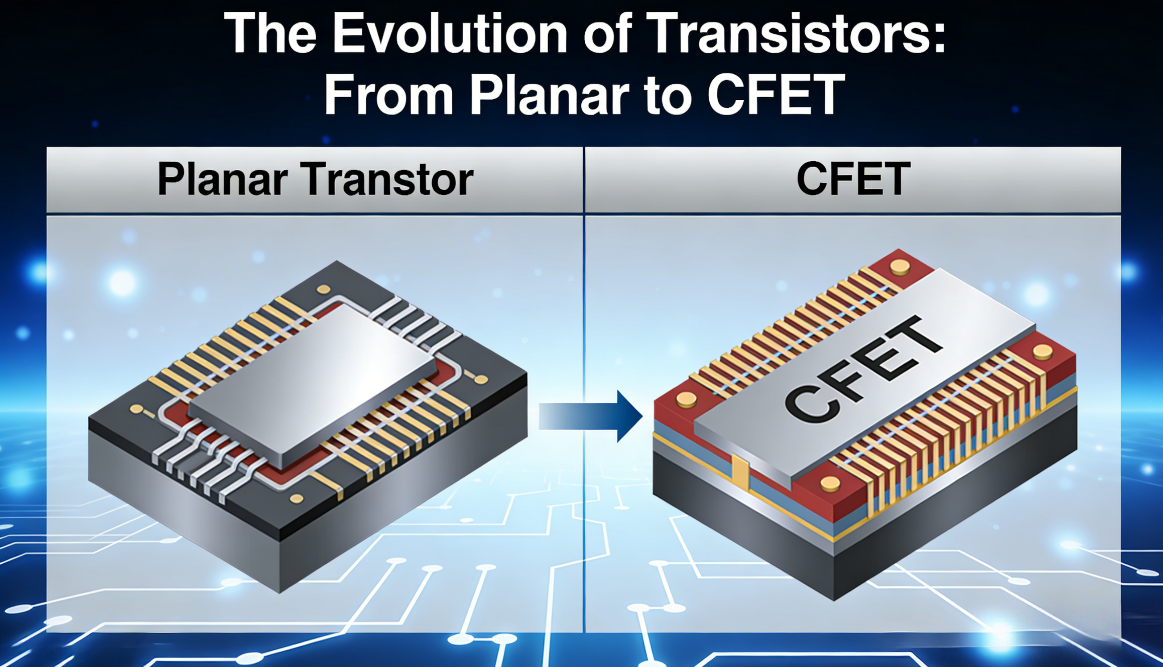

Selve transistoren gjennomgår en fullstendig arkitektonisk revolusjon.Fra plan MOSFET til FinFET, fra GAA nanoark til CFET-stabling, representerer hvert trinn et skifte fra krymping til gjenoppbygge transistoren i tre dimensjoner.Dette er ikke bare inkrementell forbedring – det er en fullstendig redefinering av hvordan brikker leverer ytelse.

De fire generasjonene av transistorarkitektur

1. Plan transistor (tradisjonell 2D)

Den klassiske flate strukturen, hvor porten styrer kanalen ovenfra.Den dominerte fra de første dagene ned til 40nm og 28nm.Etter hvert som dimensjonene krympet ytterligere, ble lekkasjestrøm og elektrostatisk kontroll uløselige problemer.

2. FinFET (3D-portkontroll)

Kanalen blir en vertikal "finne", med porten som vikler seg rundt tre sider.Dette forbedrer den elektrostatiske kontrollen drastisk, reduserer lekkasje og muliggjør nedskalering til 7nm, 5nm og til og med 3nm.FinFET ble grunnlaget for den moderne høyytelses chip-æraen.

3. GAA Nanosheet (Gate-All-Around)

Ved 2nm og under, treffer FinFET sin grense.GAA erstatter finnen med stablede horisontale nanotråder eller ark, helt omgitt av porten.Den gir bedre kontroll, lavere effekt og høyere kjørestrøm.GAA er nå mainstream-strukturen for 2nm-klasse brikker på tvers av TSMC, Samsung og Intel.

4. CFET (komplementær FET)

Den neste grensen: stabling av NMOS og PMOS vertikalt.CFET pakker to transistorer inn i fotavtrykket til én, noe som drastisk reduserer arealet og forbedrer tettheten.Det er den ultimate evolusjonære enden av transistorskalering før ekte 3D-systemintegrasjon tar over.

Hvorfor skalering alene ikke lenger fungerer

- Prosesskostnadene øker eksponentielt ved hver ny node

- Kvantelekkasje og fysiske begrensninger herder grensene

- Sammenkoblingsforsinkelse og strømforbruk overgår transistorhastigheten

- Store monolittiske flis lider av lavt utbytte og høye kostnader

Industrien har innsett: ytelsen kommer ikke lenger fra mindre transistorer.Det kommer fra bedre tilkoblinger, smartere arkitektur og vertikal integrasjon.

The New Era: Tre lag med 3D-innovasjon

Halvlederfremdrift er nå definert av tre dimensjoner av 3D-design:

- 3D transistor: FinFET, GAA, CFET – bygger transistoren vertikalt

- 3D-enhetsstabling: Minne på logikk, hybridbinding, SRAM-stabling

- 3D-systemintegrasjon: Chiplet, 2,5D/3D-emballasje, interposer-basert integrasjon

Sammen danner de 3D×3D×3D æra: transistoren, enheten og systemet blir alle tredimensjonale.

DTCO: Den nye kjernekompetansen

Når skaleringen avsluttes, Design Technology Co-Optimization (DTCO) blir kritisk.Det betyr å samdesigne arkitektur, transistorstruktur, metallruting og pakking fra starten.De sterkeste selskapene er ikke lenger bare prosessledere – de er integratorer på systemnivå.

Kablingseffektivitet, strømforsyning, termisk design og båndbreddetetthet bestemmer nå reell produktytelse.

AI er den ultimate drivkraften

AI og høyytelses databehandling krever enestående båndbredde, energieffektivitet og tetthet.Disse kravene kan ikke oppfylles ved tradisjonell skalering.De krever:

- Minne-databehandling med ultrahøy båndbredde

- Ekstrem energieffektivitet per operasjon

- Massiv parallellitet og tett integrasjon

AI har tvunget hele industrien til å forlate ren skalering og omfavne full 3D heterogen integrasjon.

Konklusjon: Fremtiden er ikke mindre, den er høyere

Tiden for krympende transistorer forsvinner.Fremtiden til halvledere handler ikke om å gjøre enheter mindre – det handler om å bygge systemer høyere, tettere og mer intelligent tilkoblet.

Fra Planar til FinFET til GAA til CFET, har transistoren fullført sin utvikling.Den neste kampen vil bli utkjempet 3D-integrasjon, avansert pakking og design på systemnivå.Det er her det neste tiåret med halvlederledelse skal avgjøres.